深入了解ESD:它們如何損害半導體元件,該如何預防?

ESD(靜電放電)的基本概念

靜電放電(ESD, Electrostatic Discharge)是由帶有靜電電荷的物體之間的電荷轉移所引發的現象。這種現象通常發生於兩個電勢不同的物體在接觸或靠近時,因靜電的快速釋放而導致電流瞬間流動。ESD 是電子設備製造和應用中的一項關鍵問題,可能導致電子元件的損壞或性能降低。

ESD損害:它如何影響半導體元件?

靜電放電(ESD)是指電荷在兩個物體之間瞬間釋放的現象,會對半導體元件產生顯著影響。由於半導體元件內部結構微小且精密,ESD 的瞬間高電壓和電流可能導致永久性損壞、功能退化甚至潛在失效。

ESD(靜電放電)會導致多種故障類型,這些故障可分為即時性損壞和潛在性損壞兩類。

以下是常見的 ESD 故障類型:

- 熱損壞:高電流在元件內部產生極高的瞬時熱量,導致金屬層熔化或燒斷。

- 電場擊穿:高電壓超過元件內部絕緣材料(如氧化層)的擊穿電壓,導致絕緣層永久損壞。

- 介電層損壞:靜電放電導致介電層的結構性損傷或物理裂痕。

- 金屬熔化或電弧燒灼:ESD 引發的瞬時大電流造成金屬導體的局部熔化或燒灼。

- 晶體管損壞:靜電放電在晶體管內部誘發高電壓或高電流,破壞其結構。

- 邏輯錯誤:靜電放電引發的高頻脈衝干擾元件的邏輯電路。

- 瞬態失效:靜電放電引發暫時性的功能中斷,但元件結構未受永久性損壞。

- 潛在損壞(Latent Damage):靜電放電雖未導致元件即時失效,但在內部留下隱性缺陷。

- 輸入/輸出接口損壞:ESD 對元件的 I/O 接口產生直接損壞。

- 電磁干擾(EMI)引發故障:靜電放電產生的高頻電磁脈衝干擾周圍元件的工作。

ESD保護的常見技術與方法

- 環境控制技術:增加空氣濕度&防靜電地板

- 設備保護技術:接地系統&靜電消除設備

- 個人防護技術:防靜電手環&防靜電鞋&防靜電服裝

- 設計防護技術:防護元件&ESD 保護電容&電路設計優化

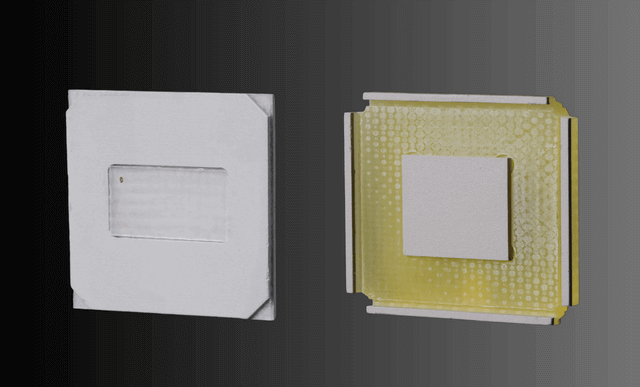

- 包裝與運輸保護:防靜電包裝&防靜電泡棉& 防靜電容器

- 測試與監控技術:靜電監測&定期測試

ESD 防護技術結合了環境控制、設備保護、個人防護和設計優化。通過實施上述技術與方法,可以顯著降低 ESD 對半導體元件和電子設備的影響,提升產品的質量與可靠性,並減少生產損失和市場退貨率。

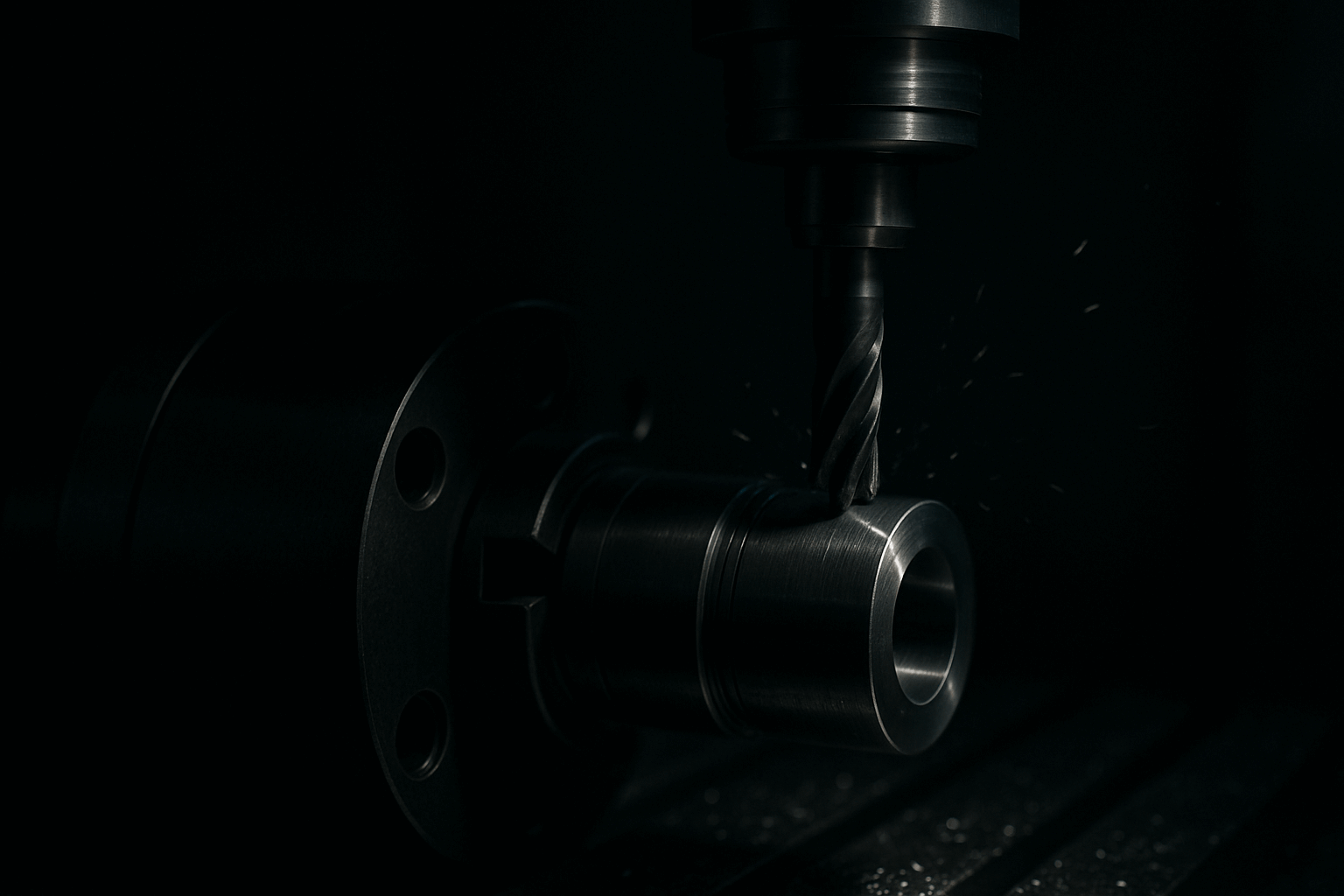

品捷ESD Coating技術

ESD Coating(靜電消散塗層)技術在防止靜電放電對元件的損害方面發揮了關鍵作用

有效防止靜電破壞: 該塗層能有效防止靜電對元件的破壞,提高產品的可靠性。

優異的導電性能: 塗層的表面電阻值範圍在 1×10⁵Ω 至 1×10⁹Ω 之間,確保靜電能迅速消散。

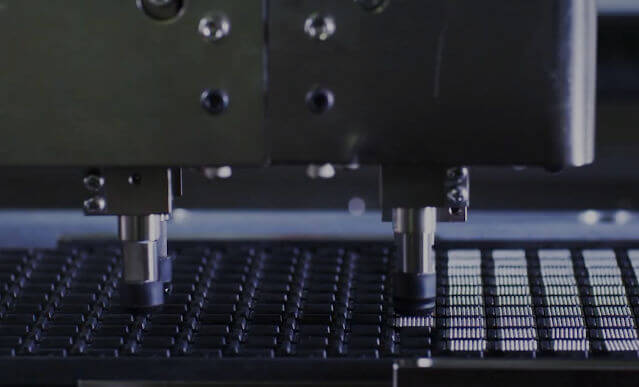

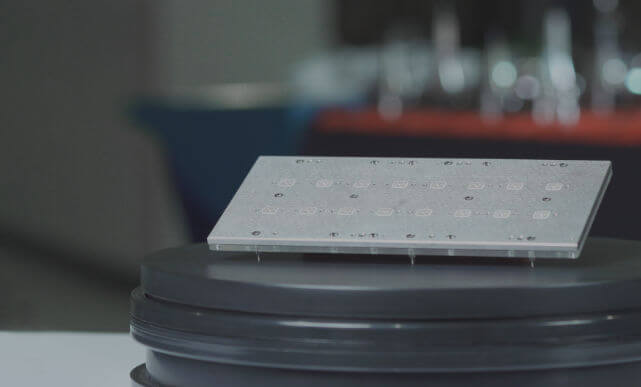

適用於多種測試治具: 品捷的 ESD Coating 可應用於各類測試治具,包括 IC 測試插座、測試板等,滿足不同客戶的需求。

透過先進的 ESD Coating 技術,品捷精密致力於為客戶提供高品質的靜電防護解決方案,確保半導體測試過程的安全與可靠

ESD測試與驗證怎麼做

ESD(靜電放電)測試與驗證旨在評估電子元件或設備在靜電環境中的抗性,確保其在設計應用場景中的可靠性。

評估抗靜電性能: 確定產品能否承受特定的靜電放電條件。

驗證設計合規性: 確保產品符合行業標準(如 IEC、ANSI 等)。

確保可靠性: 減少因靜電引發的產品失效

ESD 測試與驗證是保障電子產品質量和可靠性的核心步驟。通過選擇合適的測試模型、執行標準化測試流程並進行設計優化,可以有效減少靜電放電對元件和設備的影響,提升產品的市場競爭力與用戶信任度。

ESD與EOS的差異

| 項目 | ESD(靜電放電) | EOS(電氣過應力) |

|---|---|---|

| 定義 | 靜電荷積累後在兩個物體之間快速釋放的現象。 | 超過元件額定電壓或電流條件的持續電氣應力。 |

| 持續時間 | 短暫,通常為納秒級。 | 較長,從微秒到數秒不等。 |

| 特性 | 短時間的高電壓和瞬間放電。 | 長時間的過高電壓或電流應力 |

| 電壓/電流特性 | 瞬時高電壓、低電流。 | 高電壓、高電流,超過元件的額定範圍。 |

| 影響範圍 | 局部損壞,通常集中在接觸點。 | 廣泛損壞,可能影響整個元件或系統。 |

| 項目 | ESD 預防 | EOS 預防 |

| 環境控制 | 增加濕度(40%~60%),降低靜電積累的可能性。 | 確保電源系統穩定,避免過壓和突波。 |

| 設備保護 | -使用防靜電設備(如防靜電地板、靜電消除器)。 | -在電路中加入過壓保護元件(如TVS二極體)。 |

| -包裝使用防防靜電材料(如屏蔽袋)。 | -增加過流保護元件(如保險絲)。 | |

| 人員防護 | -佩戴防靜電手環和鞋,防止人體靜電。 | -檢查接地系統,避免接地不良引起的故障。 |

| 設計優化 | -增加ESD防護電路(如旁路電容、TVS二極體)。 | -優化電路設計,避免長時間超載情況。 |

-

Head in Pillow 枕頭效應常見成因與解決方法

2024.12.27

Head in Pillow 枕頭效應常見成因與解決方法

Head-in-Pillow (HIP) 是 BGA 焊接過程中的一種常見失效模式,指的是 BGA 焊球與焊盤之間未完全熔合,形成類似「枕頭與頭」的結構。這種缺陷會導致接觸不良,影響電子元件的性能和可靠性。

2024.12.27

Head in Pillow 枕頭效應常見成因與解決方法

Head-in-Pillow (HIP) 是 BGA 焊接過程中的一種常見失效模式,指的是 BGA 焊球與焊盤之間未完全熔合,形成類似「枕頭與頭」的結構。這種缺陷會導致接觸不良,影響電子元件的性能和可靠性。

-

晶圓測試

2024-12-23

晶圓測試

晶圓測試(Wafer Testing)是半導體製造過程中不可或缺的環節,負責檢驗晶圓上每個晶粒(Die)的功能和性能。該步驟通常在封裝前進行,目的是在不浪費資源的前提下篩選出符合設計規範的良品晶粒。

2024-12-23

晶圓測試

晶圓測試(Wafer Testing)是半導體製造過程中不可或缺的環節,負責檢驗晶圓上每個晶粒(Die)的功能和性能。該步驟通常在封裝前進行,目的是在不浪費資源的前提下篩選出符合設計規範的良品晶粒。

-

如何清潔 Pogo Pin

2024-12-20

如何清潔 Pogo Pin

Pogo Pin 是半導體測試設備中常用的彈性探針,用於在測試過程中與電子元件建立穩定的電氣連接。隨著使用頻率的增加,Pogo Pin 容易因污染物(如氧化物、焊錫殘留或灰塵)導致接觸不良,進而影響測試結果的準確性和效率。

2024-12-20

如何清潔 Pogo Pin

Pogo Pin 是半導體測試設備中常用的彈性探針,用於在測試過程中與電子元件建立穩定的電氣連接。隨著使用頻率的增加,Pogo Pin 容易因污染物(如氧化物、焊錫殘留或灰塵)導致接觸不良,進而影響測試結果的準確性和效率。

-

BGA(球柵陣列)焊接製程:缺陷及解決方案

2024-12-20

BGA(球柵陣列)焊接製程:缺陷及解決方案

BGA 焊接過程中可能出現多種缺陷,如空洞、橋接、偏移、裂紋等。這些缺陷可能源於焊接材料、設備參數、工藝設計或存儲條件等方面。通過優化材料選擇、改進工藝參數和加強質量控制,可以顯著降低焊接缺陷發生率,提升產品的可靠性與使用壽命。

2024-12-20

BGA(球柵陣列)焊接製程:缺陷及解決方案

BGA 焊接過程中可能出現多種缺陷,如空洞、橋接、偏移、裂紋等。這些缺陷可能源於焊接材料、設備參數、工藝設計或存儲條件等方面。通過優化材料選擇、改進工藝參數和加強質量控制,可以顯著降低焊接缺陷發生率,提升產品的可靠性與使用壽命。

-

半導體中的最終測試是什麼?

2024-06-27

半導體中的最終測試是什麼?

在半導體製造過程中,最終測試(Final Test,簡稱FT)是一個關鍵步驟,它確保每個晶片在出廠前達到預期的性能標準。

2024-06-27

半導體中的最終測試是什麼?

在半導體製造過程中,最終測試(Final Test,簡稱FT)是一個關鍵步驟,它確保每個晶片在出廠前達到預期的性能標準。

-

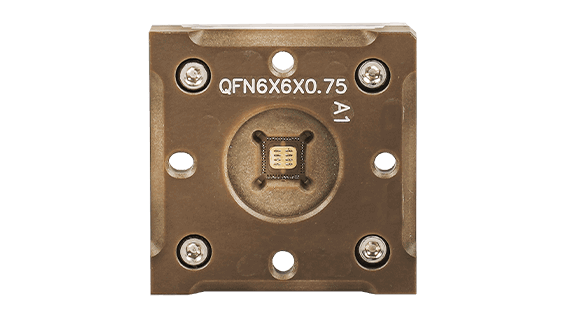

QFN Socket 插座是什麼?

2024-06-12

QFN Socket 插座是什麼?

QFN(Quad Flat No-lead)插槽是一種無引腳扁平封裝類型,用於集成電路的表面貼裝。

2024-06-12

QFN Socket 插座是什麼?

QFN(Quad Flat No-lead)插槽是一種無引腳扁平封裝類型,用於集成電路的表面貼裝。

-

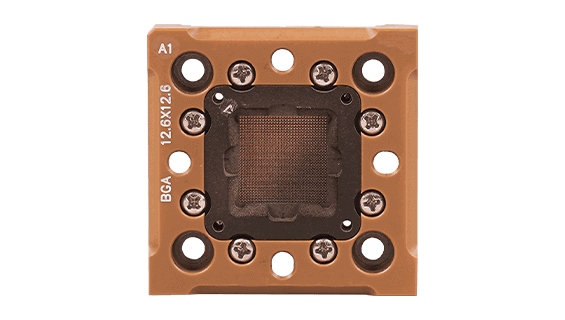

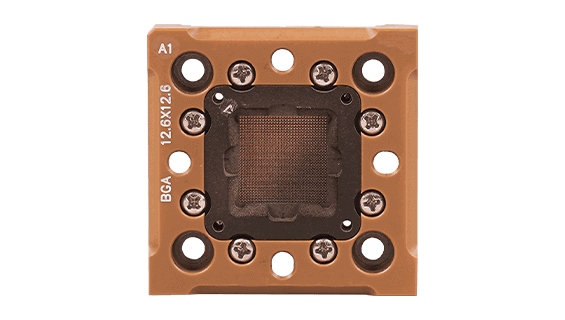

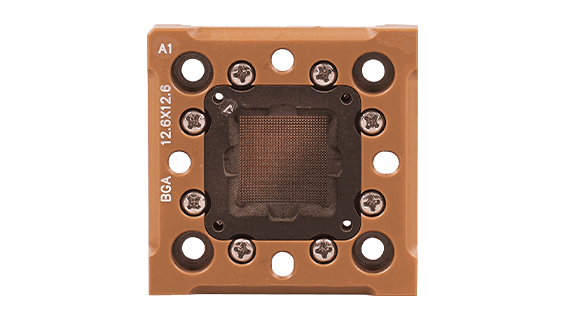

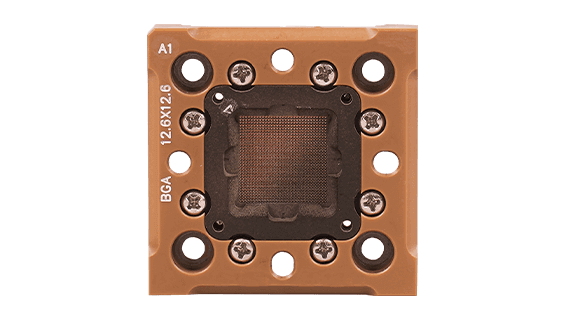

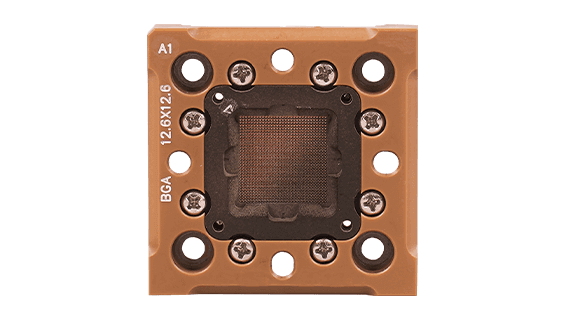

BGA Socket 插座是什麼?

2024-06-05

BGA Socket 插座是什麼?

BGA插槽(Ball Grid Array插槽)是一種用於集成電路的表面貼裝封裝類型。

2024-06-05

BGA Socket 插座是什麼?

BGA插槽(Ball Grid Array插槽)是一種用於集成電路的表面貼裝封裝類型。

-

Test Sockets:IC測試中的關鍵元件

2024-05-29

Test Sockets:IC測試中的關鍵元件

本文將深入探討Test Sockets的重要性、類型及其在半導體行業中的應用。

2024-05-29

Test Sockets:IC測試中的關鍵元件

本文將深入探討Test Sockets的重要性、類型及其在半導體行業中的應用。